Product Summary

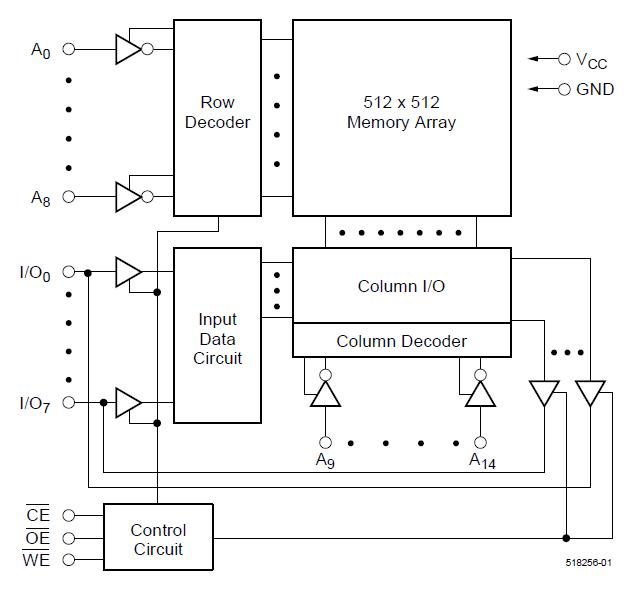

The V62C518256LL-70 is a 262,144-bit static random access memory organized as 32,768 words by 8 bits. It is built with MOSEL VITELIC’s high performance CMOS process. Inputs and threestate outputs are TTL compatible and allow for direct interfacing with common system bus structures.

Parametrics

V62C518256LL-70 absolute maximum ratings: (1)VCC, Supply Voltage: -0.5 to +7 V; (2)VN, Input Voltage: -0.5 to +7 V; (3)VDQ, Input/Output Voltage Applied: VCC + 0.5 V; (4)TBIAS, Temperature Under Bias: -65 to +135℃; (5)TSTG, Storage Temperature: -65 to +150℃.

Features

V62C518256LL-70 features: (1)High-speed: 35, 70 ns; (2)Ultra low DC operating current of 5mA (max.); (3)Low Power Dissipation: TTL Standby: 3 mA (Max.); CMOS Standby: 20mA (Max.); (4)Fully static operation; (5)All inputs and outputs directly compatible; (6)Three state outputs; (7)Ultra low data retention current (VCC = 2V); (8)Single 5V ±10% Power Supply; (9)Packages, 28-pin TSOP (Standard); 28-pin 600 mil PDIP; 28-pin 330 mil SOP (450 mil pin-to-pin).

Diagrams

|

V62C1161024L |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

V62C1161024L(L) |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

V62C1162048L(L) |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

V62C1164096 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

V62C1801024L(L) |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

V62C1802048L(L) |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))